ARTICLE

# CROSS TALK AVOIDANCE AND ERRORCORRECTION CODES THROUGH RELIABLE NETWORKS ON CHIP USING HYBRID RECONFIGURABLE ARCHITECTURE

VA. Saravanan<sup>1</sup>\*, K. Paramasivam<sup>2</sup>

<sup>1</sup>AP/ECE, ASL Paul College of Engineering and Technology, Coimbatore, Tamilnadu, INDIA <sup>2</sup>Dept of ECE, Kumaraguru College of Technology, Coimbatore, Tamilnadu, INDIA

### ABSTRACT

In Traditional techniques, Messages in the NoC are exchanged with a wormhole slice through exchanging strategy; whereas various messages can be interleaved at bounce level in a similar correspondence interface without utilizing virtual channels. Advance in 3D NoCs basically utilize a deterministic directing calculation to convey bundles from a source to a goal hub. In any case, deterministic strategies can't disperse the activity stack over the system, which brings about debasing the execution. In this paper, with a specific end goal to increment in the unwavering quality of Network-on-chip by keeping away from blunders and crosstalk between the switches presents the outline of a NoC switch in view of turn model. A Turn Model directing calculation is utilized to maintain a strategic distance from deadlock clashes. Additionally the switch coordinates a dynamic authority to build the Quality of Service of system. Promote Crosstalk Avoiding Double Error Correction Scheme Encoder is a basic mix of Hamming coding took after by The Duplicate Add Parity (DAP) or Boundary Shift Coding (BSC) encoding to give insurance against cross talk, here in this paper we have joined two calculations and made configurable building outline. Additionally hamming codec is utilized for identification and mistake revision other than crosstalk evasion CODEC for staying away from the crosstalk in the middle of the switches of the NoC. In our work, 2D/3D switch configuration is broke down utilizing Xilinx 13.2 whereas results examination accomplished for delay and frequency in satisfied manner. The significance of 3D model is to expand the layers in the topology, which in increment the rate of availability that makes the NoC minimal in size.

## INTRODUCTION

KEY WORDS

3D network, fully adaptive routing, Duplicate Add Parity, Boundary Shift Coding (BSC)

Received: 16 Dec 2017 Accepted: 03 Jan 2018 Published: 6 Jan 2018

\*Corresponding Author Email: msg2saravana@gmail.com Tel.: 9894459731

The customary high clock rate single center frameworks have been supplanted by conveyed many-center frameworks on a solitary bite the dust because of vitality utilization and execution limits. Information transmission through a chip is viewed as more difficult since worldwide interconnects are turning into the foremost execution bottle-neck for superior systems. System-on-Chip (SoC) does not bolster future innovations as the quantity of centers on single kicks the bucket increments. Network on-Chip (NoC) has been proposed as another interconnection design to sup-port better particularity, versatility and higher transmission capacity highlights. Control scattering is getting to be distinctly basic constraints of framework plan because of battery lifetime, cooling, and warm spending plans concerns. It has been accounted for that system control for a many-center pass on later on can be as high as 150W, assuming current system scale usage. Reducing vitality devoured in NoC is of extraordinary significance for superior and vitality efficient designs. Routing is a basic piece of NoC, and has a significant effect on the correspondence efficiency, particularly if there should arise an occurrence of single-flit packets Various disseminated directing calculations have been proposed for NoC/SoC platforms. An versatile dispersed steering calculation for 2D work SoC/NoC is exhibited, which depends on Dynamic XY (DyXY) [1]. A conveyed directing calculation is displayed with no steering. In [2] an appropriated defeating calculation for a 3D NoC is introduced. As per the Technology Roadmap for Semiconductors (ITRS), There-Dimensional (3D) mix is viewed as a promising advancement to keep up the execution change past 65nm [3]. In 3D blend development, various element silicon layers are stacked together using Through-Silicon-Vias (TSVs).[4] The genuine favored angle of 3D ICs is the noteworthy diminishment in the impression and overall inter connect length, resulting in extended execution [5]. 3D Networks-on-Chip (3D NoCs), of course, are creating as a response for the inter connect multifaceted design in 3D SoCs [6].Routing estimations are used to thruway a package from a source to an objective. Controlling figurings can be gathered by where coordinating decisions are taken [7]. In a source coordinating [8], the way can be developed at the source center before the package implantation while in a circled directing, the way is settled dispersedly while the package navigated the framework. Not in the slightest degree like scattered guiding, in the source coordinating strategy, the way information is passed on by packs, thus switches does not require any extra estimation for settling on directing decisions. This results in a less troublesome guiding unit and a snappier correspondence. In any case, as groups are required to pass on the way information (i.e. that is for the most part broad), the exchange speed essential and versatility get the opportunity to be unmistakably genuine challenges. Right when spread coordinating is used, the way is figured at each widely appealing center point. Passed on guiding can be portrayed into deterministic and adaptable [9]. A deterministic controlling figuring uses a settled path for each join of source and objective centers. Utilization of deterministic guiding computations are direct anyway they can't conform the pile over the associations. The slightest troublesome deterministic guiding methodology is estimation mastermind coordinating. The estimation organize guiding computation courses packages by crossing point estimations in completely growing solicitation, reducing the balance in one making a beeline for zero going before coordinating in the accompanying one. Deterministic directing estimations perform well with uniform development plan while they are astoundingly inefficient under non-uniform movement.[10] Curiously, in adaptable coordinating computations, a package is not restricted to a singular way while going from a source center to its objective. Thusly, adaptable controlling estimations can lessen the

7

probability of coordinating packages through congested regions. Several midway and totally flexible directing counts are introduced in 2D frameworks, for instance, DyXY [11] and Odd-Even [12]. The coordinating assurance of these figuring is regularly performed using the blockage status of the framework. A noteworthy number of them consider neighborhood development condition in the directing decision in which each switch examinations the obstruct conditions of its own and close-by changes to pick a vield channel. This social occasion of computations could upgrade the execution out and out when diverged from estimation organize directing due to the spread of packages over the framework. In any case, coordinating decisions in light of close-by blockage information may provoke to an unbalanced distribution of development load. Some unique figurings, for instance, obstruct careful trapezoid-based guiding algorithm (CATRA) [13] and Highly Adaptive Routing Algorithm in On-Chip Networks (HARAQ) [14] consider more overall information, diminishing the probability of settling on a wrong decision. In any case, paying little personality to the constrained multifaceted nature and range overhead, giving overall information is eccentric. In total, adaptable coordinating computations in perspective of overall blockage information upgrade the execution over the procedures in light of adjacent stop up information. This execution get is at the cost of an enormous zone overhead, a more capricious coordinating unit, and the prerequisite for stop up area and spread framework. There are few for the most part adaptable systems showed in 3D NoCs, for instance, metal relic diminishment (MAR)[15].

In this paper, 2D switch is our talked about in the segment II alongside 3D directed plan rule. Encourage the proposed strategy alongside 3D switch model is dissected in the segment III alongside arrangement which defeats the downsides of the current technique is examined. In area IV results are looked at and downsides are examined The significance of 3D model, investigated to expand the layers in the topology which wills increment the rate of openness that makes NoC minimal in size and Section V gives out the conclusion.

## EXISTING METHOD

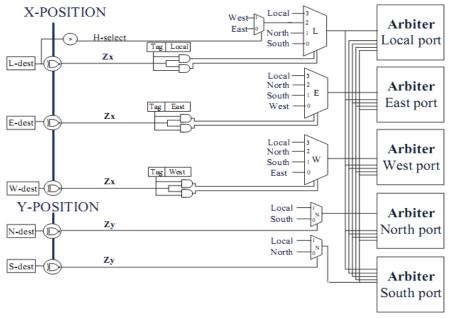

[16] In the conventional method Runtime Contention and Bandwidth-Aware Adaptive Routing Selection Strategies for Networks-on-Chip is analysed whereas This paper presents adaptive routing selection strategies suitable for network-on-chip (NoC). Messages in the NoC are switched with a wormhole cutthrough switching method, where the different messages can be interleaved at flit-level in the same communication link without using virtual channels. On the Design of Hybrid Routing Mechanism for Meshconstruct thoroughly Network-with respect to Chip the Tag NoC helps all turn adaptation directing calculations, for example, four surely understood ones like XY, NF, WF and NL. Since XY directing calculation is the reference show for the greater part of the NoC related re-look for, This Tag NoC coding values and comparing multiplexer selectors are intended for this [17]set of rules. This configuration bolsters 2D NoC Only with the Ports: North, South, East, West as demonstrated in the [Fig. 1].

Fig. 1: Design of hybrid routing mechanism for mesh-based network-on-chip

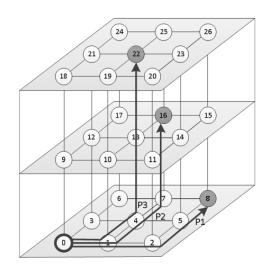

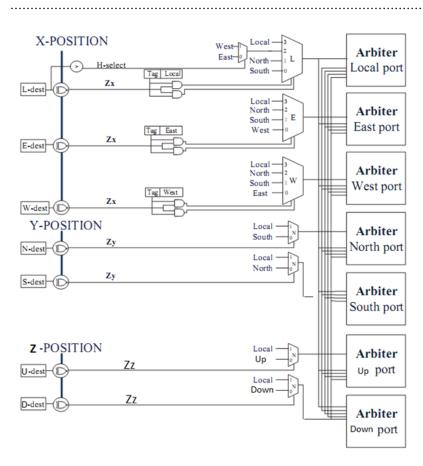

Further, the Fully Adaptive Routing Algorithm for 3D NoCs is analyzed with the Ports: North, South, East, West, Up, Down which is shown in the [Fig. 2] along with the 3D model structure is described below.

| Direction | Virtual Channels |

|-----------|------------------|

| ENU       | X0,Y0,Z0         |

| END       | X1,Y1,Z1         |

| ESU       | X2,Y0,Z0         |

| ESD       | X3,Y1,Z1         |

| WNU       | X0,Y2,Z0         |

| WND       | X1,Y3,Z1         |

| WSU       | X2,Y2,Z0         |

| WSD       | X3,Y3,Z1         |

| EN        | (X0,X1),(Y0,Y1)  |

| ES        | (X2,X3),(Y0,Y1)  |

| EU        | (X0,X2),(Z0)     |

| ED        | (X0,X3),(Z1)     |

| WN        | (X0,X1),(Y2,Y3)  |

| WS        | (X2,X3),(Y2,Y3)  |

| WU        | (X0,X2),(Z0)     |

| WD        | (X1,X3),(Z1)     |

| NU        | (Y0,Y2),(Z0)     |

| ND        | (Y1,Y3),(Z1)     |

| SU        | (Y0,Y2),(Z0)     |

| SD        | (Y1,Y1),(Z1)     |

| E         | (X1,X2,X3,X4)    |

| W         | (X1,X2,X3,X4)    |

| N         | (Y0,Y1,Y2,Y3)    |

| S         | (Y0,Y1,Y2,Y3)    |

| U         | (Z0,Z1)          |

| D         | (Z0,Z1)          |

## Fig. 2: Adaptive routing algorithm

# Fig. 3: 3D model structure

As shown in the [Fig. 3] [18], NoC ensures high performance and scalability. To overcome those limitations, in this paper we presents the design of a NoC router based on hybrid model where Turn model and Fully Adaptive Routing Algorithm is combined together which gives reconfigurable architecture. A Turn Model routing algorithm is used to avoid deadlock conflicts. Also the router integrates a dynamic arbiter to increase the Quality of Service of network. Crosstalk avoiding double error correction code (CADEC) is used

#### www.iioab.org

to for cross talk avoidance. To evaluate performance of our design, we compared it with various routers in terms of delay, power and clock frequency.

# PROPOSED METHOD

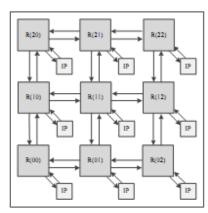

Runtime Contention and Bandwidth-Aware Adaptive Routing Selection Strategies for Networks-on-Chip. The above structures were joined and 1/2 breed reconfigurable interpretation is proposed with the hope to grow the unwavering quality of Network-on-chip by staying far away from misunderstandings and crosstalk among the switches. As showed up inside the [Fig. 4]. In the 1/2 and half of model Design of a Network-on-Chip move in tender of flip frame praised the plan of a NoC move in light of flip model. A Turn Model organizing calculation is associated with stay faraway from expect clashes. Additionally the switch passes on an element go between to make more noteworthy the Quality of Service of device. The trade parameters are chosen underneath for the 2D represents.

| • | Router Parameters | 2D router         |

|---|-------------------|-------------------|

| • | Buffer Depth      | 4                 |

| • | Flit size (bit)   | 32                |

| • | Switching         | wormhole          |

| • | Flow control      | Credit based      |

| • | Scheduling        | Dynamic arbiter   |

| • | Routing           | Negative-First    |

| • | Target device     | Virtex5 XC5VFX70T |

The arbiter module of the switch allocator uses a round-robin and a priority scheduler schemes to assign the highest priority packet to the adequate output port. The turn model which is a deadlock-free partial adaptive routing algorithm for mesh NoC.

Fig. 4: 3x3 NoC model

.....

Cross talk avoidance can be done through crosstalk avoiding double error correction code (CADEC) In wormhole exchanging, the halt circumstance happens when bundles are sitting tight for each other in cyclic conditions. In 2D work arrange, switches may forward parcels in four bearings: North, East, South and West. Bundles may take eight turns for every bearing. A hand over this setting alludes to a change of 90-level of the voyaging bearing of the parcel. The negative-first turn demonstrate steering calculation is picked because of its versatility and effortlessness.

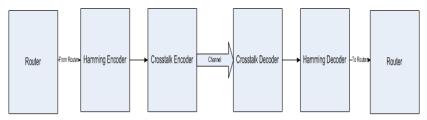

In the half and half model the Crosstalk shirking and mistake amendment is handled through Crosstalk Avoiding Double Error Correction Scheme Encoder The encoder is a basic mix of Hamming coding took after by DAP or BSC encoding to give security against cross talk.

· Boundary Shift Coding (BSC) is accomplished by keeping away from a common limit between two progressive code words.

• The Duplicate Add Parity (DAP) plot accomplishes joint crosstalk evasion and single blunder rectification capacity by copying every piece of the n-bit flutter and putting the duplicates contiguous each other to evade crosstalk, and by additionally figuring an equality bit from the underlying bits to empower single mistake adjustment.

The unraveling calculation comprises of the accompanying straightforward strides

- The equality bits of the individual Hamming duplicates are ascertained and contrasted and the sent 1. equality:

- 2. If these two equalities acquired in step 1 vary, then the copy whose equality matches with the transmitted equality is chosen as the yield cop y of the primary stage.

- If the two equalities are equivalent, then any one duplicate is sent forward for disorder identification. 3.

ENGINEERING

10

- If the disorder got for this duplicate is zero then this duplicate is chosen as the yield of the primary 4. stage. Something else, the substitute duplicate is chosen.

- 5. The yield of the principal stage is sent for (38, 32) single mistake redressing Hamming unraveling, at long last delivering the decoded CAD EC yield. As appeared in the [Fig. 5].

Fig. 5: Flow of the proposed Hybrid model

#### .....

## **RESULTS AND DISCUSSION**

#### Xilinx/ISE Simulations and Precision RTL of mentor graphics

The proposed NoC and its related blocks are depicted utilizing basic Verilog and incorporated utilizing Xilinx Synthesis Tool (XST), Web PACK form 13.2 and Precision RTL of Mentor Graphics. The execution was focused to Xilinx Virtex5 low power, Selected Device: Virtex5 XC5VFX70T

The consistent directing can be seen from the acquired Place and course result from the FPGA Editor alternative in Xilinx synthesizer. It is watched that higher utilization around 10% of Basic logic components (BELS) range for the focused on FPGA is secured for the execution of this System in the proposed technique because of hybrid design which can be advanced in further strategies. The configurable rationale blocks are associated in course way to get the usefulness for the outlined framework. To guarantee that the equipment usage works legitimately, simulation test was performed utilizing I-Sim (0.76.xd).

#### Impact of the proposed flow on peak frequency usage, timing and power

In this paper, the customary approach and the proposed technique is investigated in view of the cost capacity of placer and switch. As appeared in the [Table 1] the quantity of Frequency use, timing and power are diminished in proposed stream because of less utilization of intelligent circuit in the outline. As the [Table 1] appear:

The directed design of the routine and proposed technique onVirtex5 XC5VFX70T is classified in [Table 1] demonstrate the proposed technique beats the customary engineering as far as position and steering which has appeared in the [Table 1] Shows the proposed strategy decreased the postponement of 40% for the 2D however thus it indicates increment in 3D technique because of cross breed design. Promote 11%decline in recurrence use for 3D technique with contrast with traditional strategy. As far as overhead, since the customary approach and the proposed strategy just change the situation and directing of the outline, as the use of the configurable rationale squares shifts which gives the overhead in the current approach. Moreover, no inaccessible configurable rationale pieces are accounted for by the first strategy and the proposed technique which conquers the confinement of the first approach. Henceforth, the traditional approach and the proposed technique manage configurable rationale squares overhead.

The configurable rationale squares are associated in course way to get the usefulness for the outlined system. As the scope zone of the configurable rationale pieces which limit course channel width. The lower defer originates from that the quantity of glitches is littler when the bring proliferates Quicker through the rationale.

Table 1: Optimized parameter comparison for the conventional and proposed method

| Parameter           | Existing Work             |                           | Proposed Work   |                 |

|---------------------|---------------------------|---------------------------|-----------------|-----------------|

| Router              | 2D                        | 3D (proposed)             | 2D              | 3D (proposed)   |

| Buffer Depth        | 8                         | 8                         | 4               | 4               |

| Switching           | wormhole                  | wormhole                  | wormhole        | wormhole        |

| Flow control        | No                        | No                        | Credit based    | Credit based    |

| Scheduling          | No                        | No                        | Dynamic arbiter | Dynamic arbiter |

| Routing             | Dimension Ordered Routing | Dimension Ordered Routing | Negative-First  | Negative-First  |

| Error Correction    | No                        | No                        | Hamming Code    | Hamming Code    |

| Crosstalk Avoidance | No                        | No                        | CADEC           | CADEC           |

| BELS                | 146                       | 151                       | 161             | 192             |

| Power               | 252.65mW                  | 252.90mW                  | 270.68mW        | 273.58mW        |

| Delay               | 2.739ns                   | 2.964ns                   | 2.370ns         | 3.348ns         |

| Maximum Frequency   | 365.050MHz                | 337.388MHz                | 421.971MHz      | 298.663MHz      |

11

#### Total on chip power

Power dissipation is mainly due to switching power, short-circuit and leakage power.

P

ower=

$$P_{switching} + P_{shortcircuit} + P_{leakage}(1)$$

Switching activity factor: a

If the signal is a clock,  $\alpha = 1$  then If the signal switches once per cycle,  $\alpha = \frac{1}{2}$  besides For Dynamic gates: switch is either 0 or 2 times per cycle,  $\alpha = \frac{1}{2}$  and for the Static gates: depending on design, but typically  $\alpha$ = 0.1

$P_{switching} = \alpha . f. C_{eff} . V_{dd}2$ (2)

Where α is the probability of a signal transition with in clock period, Ceff indicates the effective capacitance is the clock frequency and  $V_{dd}$  is the power supply voltage.

Short-circuit power occurred when there is a transition between VDD and GND occurs

Pshortcircuit = lsc .Vdd.f

$P_{leakage} = f(V_{dd}, V_{th}, W/L)$

(4)Power consumption has calculated following this formula As shown in the [Table 1].

(3)

$$\boldsymbol{p} = \boldsymbol{v}\boldsymbol{d}\boldsymbol{d}.\frac{\int_0^I \boldsymbol{I}_{\boldsymbol{d}\boldsymbol{d}}}{\boldsymbol{\tau}}$$

(5)

Where V<sub>dd</sub> is the supply voltage, I<sub>dd</sub> is the supply current, and T is the period. Isc the short circuit current and f indicates the frequency. As the total power dissipation is increased due to the switching activity of the transistor. The power comparison for various styles due to switching activity has shown in the [Table 1]. The proposed design is the can be optimized further for total on chip power consumption (i.e., least amount) than over all conventional methods.

## CONCLUSION

Movement can be conveyed over the system by utilizing elective ways. In this paper, we proposed a hybrid reconfigurable architecture algorithm. In this technique, at every middle of the node hub, a message is sent to a bearing which is less congested which decreases the postponement of the proposed strategy which recorded previously. This calculation is ended up being stop by utilizing 4, 4, and 2 virtual channels along the X, Y, and Z measurements, separately. In spite of the fact that this calculation can ease the clog, it can't be utilized for the applications requesting all together conveyance for less power and territory because of congested design which can be advanced in further work. With a specific end goal to address the altogether conveyance issue in 3D organize and to lessen the power utilization and area, we are attempting to propose a strategy as a future work.

CONFLICT OF INTEREST There is no conflict of interest.

**ACKNOWLEDGEMENTS** None

FINANCIAL DISCLOSURE None

### REFERENCES

- Dubois F, Sheibanyrad A, Petrot F, Bahmani M. [2013] [1] routing Elevator-first: A deadlock-free distributed algorithm for vertically partially con-nected 3d-nocs. Computers, IEEE Transactions on, 2(3):609-615.

- [2] Flich J, Rodrigo S, Duato J. [2008] An efficient implementation of dis-tributed routing algorithms for nocs. In Networks-on-Chip. NoCS. Second ACM/IEEE International Symposium on, 87-96.

- Lotfi-Kamran P, Rahmani A, Daneshtalab M, Afzali-Kusha [3] A, Navabi Z. [2010] Edxy a low cost congestion-aware routing algorithm for network-on-chips. Journal of Systems Architecture. 56(7):256 - 264.

- [4] Rodrigo S, Medardoni S, Flich J, Bertozzi D, Duato J. [2009] Efficient implementation of distributed routing

algorithms for nocs. Computers Digital Techniques, IET. 3(5):460-475.

- [5] Pavlidis VF, Rochester Friedman EG. [2006] 3-D Topologies for Networks-on-Chip. 15(10):1081-1090.

- [6] Xu TC, et al. [2011] Optimal Number and Placement of Through Silicon Vias in 3D Network-on-Chip. In Proceedings of the 14th IEEE International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS). 105-110.

- Dane shtalab M, et al. [2012] HIB S-Novel Inter-layer Bus [7] Structure for Stacked Architectures, in Proceedings of IEEE International 3D Systems Integration Conference (3DIC). 1-7

- Ebrahimi M, et al. [2011] Exploring Partitioning Methods [8] for 3D Networks-on-Chip Utilizing Adaptive Routing Model,

in Proceedings of 5th ACM/IEEE International Symposium on Networks-on-Chip (NOCS). 73-80.

- [9] Duato J, Yalamanchili C, Ni L. [2003] Interconnection networks: an engineering approach, Morgan Kaufmann Publishers.

- [10] Mubeen S, Kumar S. [2010] Designing Efficient Source Routing for Mesh Topology Network on Chip Platforms. 181-188.

- [11] Daneshtalab M, et al. [2012] Adaptive Input-output Selection Based On-Chip Router Architecture, Journal of Low Power Electronics (JOLPE). 8(1):11-29.

- [12] Daneshtalab M, et al. [2007] Distributing Congestions in NoCs through a Dynamic Routing Algorithm based on Input and Output Selections, in Proceedings of 20th IEEE International Conference on VLSI Design (VLSID). 546-550.

- [13] Li M, Zeng Q, Jone W. [2006] DyXY a proximity congestion-aware deadlock-free dynamic routing method for network on chip, in proceedings of DAC. 849-852.

- [14] Chiu GM. [2000] the odd-even turn model for adaptive routing, IEEE Transaction on Parallel and Distributed Systems. 11:729–738.

- [15] Ebrahimi M, et al. [2012] CATRA-Congestion Aware Trapezoid-based Routing Algorithm for On-Chip Networks, in Proceedings of 15th ACM/IEEE Design, Automation, and Test in Europe (DATE). 320-325.

- [16] Ebrahimi M, et al. [2012] HARAQ: Congestion-Aware Learning Model for Highly Adaptive Routing Algorithm in On-Chip Networks, in Proceedings of 6th ACM/IEEE International Symposium on Networks-on-Chip (NOCS). 19-26.

- [17] Seitanidis I et al. [2014] ElastiStore: An elastic buffer architecture for Network-on-Chip routers. Design, Automation and Test in Europe Conference and Exhibition (DATE), 2014. Doi: 10.7873/DATE.2014.253

- [18] Mohana Priya N, Brindha G. [2016] A Survey on Routing Protocols in Wireless Sensor Networks. International Conference on Computer Applications. 38-45.